#### Corso di Calcolatori Elettronici I

# Macchine combinatorie: encoder/decoder e multiplexer/demultiplexer

**Prof. Roberto Canonico**

Università degli Studi di Napoli Federico II

Dipartimento di Ingegneria Elettrica

e delle Tecnologie dell'Informazione

Corso di Laurea in Ingegneria Informatica

Corso di Laurea in Ingegneria dell'Automazione

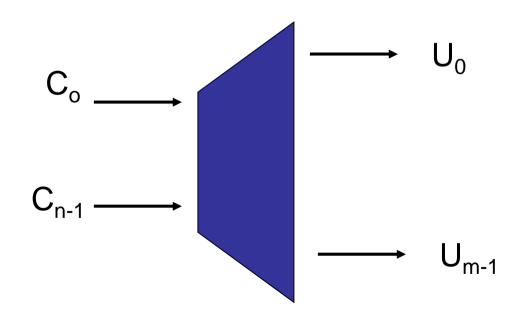

# Decodificatore (decoder) 1 su m

• Un decodificatore è una macchina che riceve in ingresso una parola codice (C) su n bit e presenta in uscita la sua rappresentazione decodificata (linee  $U_0, \dots U_{N-1}$ ) su m=2<sup>n</sup> bit

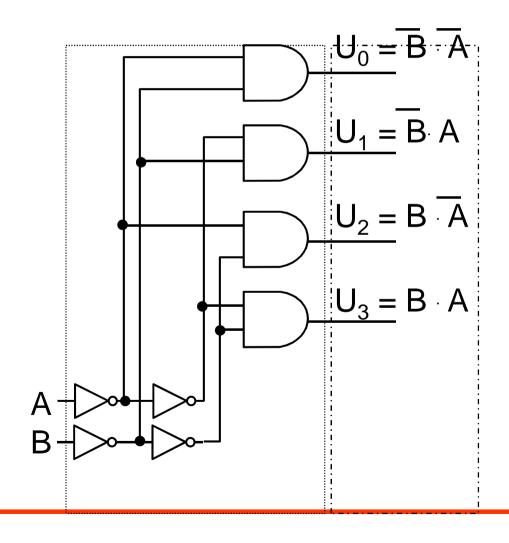

#### Decoder 1 su 4

#### Esempio: decoder 1:4

|   | В | Α | Uo | U <sub>1</sub> | $U_2$ | $U_3$ |

|---|---|---|----|----------------|-------|-------|

| 1 | 0 | 0 | 1  |                | 0     | 0     |

| 2 | 0 | 1 | 0  | 1              | 0     | 0     |

| 3 | 1 | 0 | 0  | 0              | 1     | 0     |

| 4 | 1 | 1 | 0  | 0              | 0     | 1     |

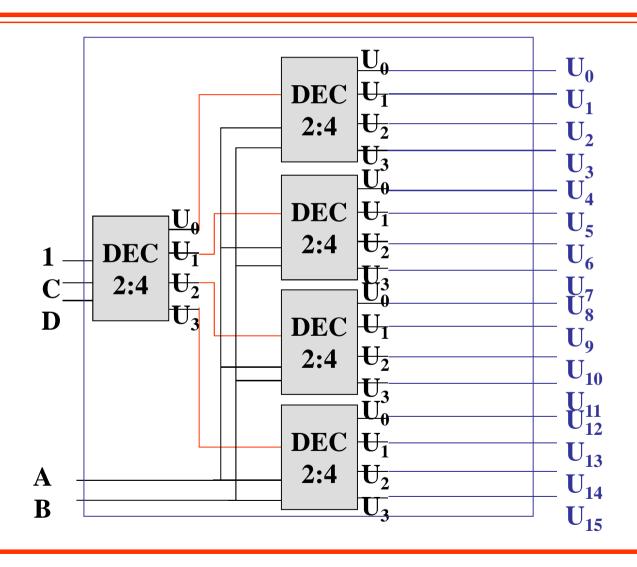

# Composizione modulare di decoder: decoder 4:16 con decoder 2:4

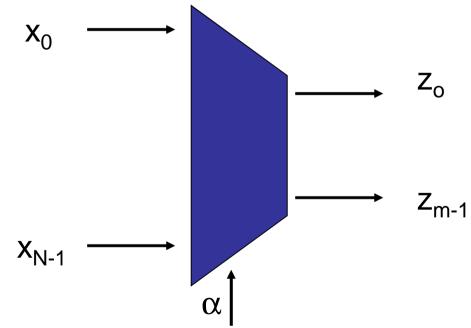

#### **Encoder o codificatore**

- Un codificatore riceve in ingresso una rappresentazione decodificata (linee  $x_0, \dots x_{m-1}$ ) e fornisce in uscita una rappresentazione con un codice a lunghezza fissa di n bit

- L'uscita è la parola codice associata a x<sub>i</sub> se x<sub>i</sub>=1 ed α=1 (abilitazione)

- Vincolo su ingressi:

$$x_i \cdot x_j = 0 \text{ per } i \neq j$$

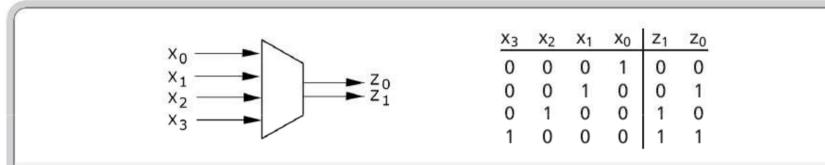

# Codificatore a 4 ingressi

Figura 3.31 - Schematizzazione di un codificatore a quattro ingressi e parte della tabella di verità delle funzioni di uscita.

#### Codificatore 8-4-2-1

•

$$z_3 = x_8 + x_9$$

•

$$Z_2 = X_4 + X_5 + X_6 + X_7$$

•

$$Z_1 = X_2 + X_3 + X_6 + X_7$$

•

$$Z_0 = X_1 + X_3 + X_5 + X_7 + X_9$$

| cifra |         |

|-------|---------|

|       | 8-4-2-1 |

| 0     | 0000    |

| 1     | 0001    |

| 2     | 0010    |

| 3     | 0011    |

| 4     | 0100    |

| 5     | 0101    |

| 6     | 0110    |

| 7     | 0111    |

| 8     | 1000    |

| 9     | 1001    |

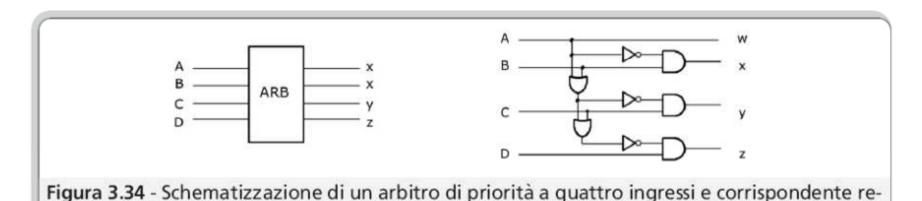

# Arbitro di priorità

- ☐ Un codificatore può essere preceduto da una "rete a priorità" che, in caso di più ingressi contemporaneamente alti, filtra quello con priorità assegnata maggiore

- Rete a priorità

- -n ingressi  $X_i$

- n uscite corrispondenti F<sub>i</sub>, che rappresentano gli ingressi del codificatore

- fra gli ingressi è definita una priorità, ad esempio:

- per fissare le idee

«X<sub>i</sub> è prioritario su X<sub>j</sub> se i < j»</li>

- L'uscita Y<sub>i</sub> è alta se e solo se X<sub>i</sub> è alto e tutti gli altri ingressi prioritari su X<sub>i</sub> sono bassi.

$$F_1 = X_1$$

$$F_2 = X_2 \overline{X_1}$$

$$F_n = X_n \overline{X_{n-1}} \dots \overline{X_1}$$

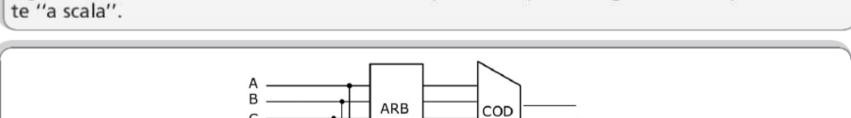

# Arbitro di priorità a 4 ingressi

Figura 3.35 - Costruzione di un codificatore di priorità a partire da un arbitro di priorità e da un codificatore. La linea INTR indica che almeno una delle linee tra A, B, C e D è 1. Quando INTR è 0, nessuna linea di ingresso risulta asserita e l'uscita del codificatore è senza significato.

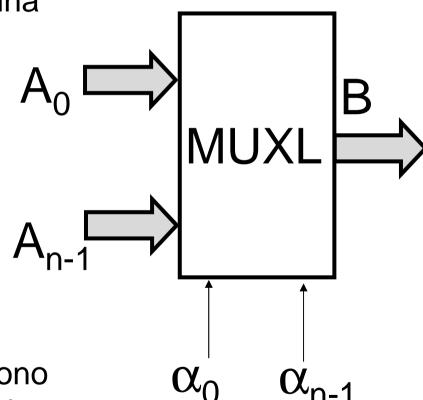

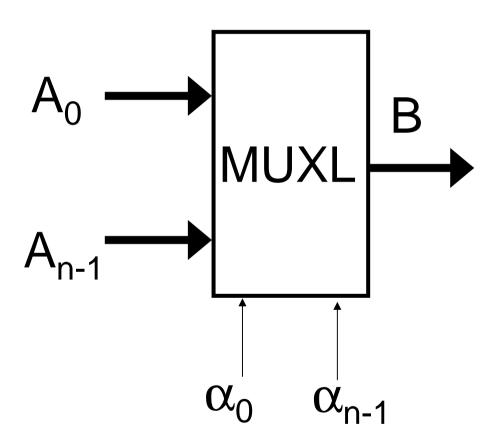

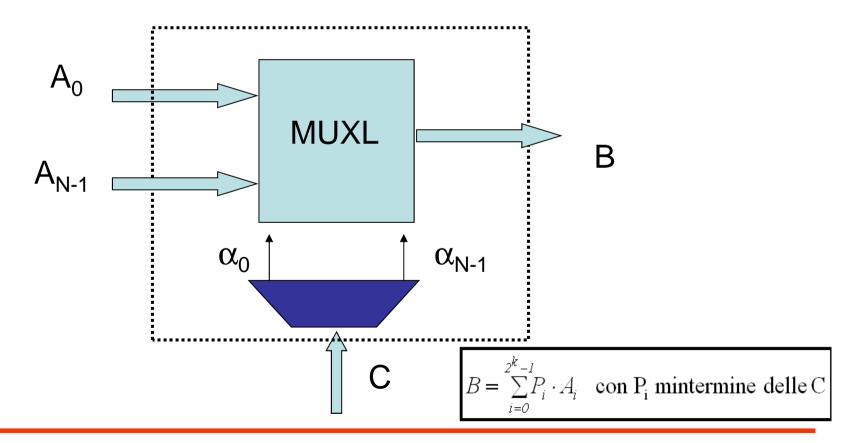

## Multiplexer lineare

Un Multiplexer lineare (ML) è una macchina con:

- n ingressi-dati  $(A_0,...,A_{n-1})$

- n segnali binari di selezione (α<sub>0</sub>,..., α <sub>n-1</sub>),

dei quali al più uno è attivo

- una uscita-dati B, che assume

- valore A<sub>i</sub> se è attivo α<sub>i</sub>

- neutro se nessuna delle selezioni è attiva

- utilizzata quando più linee devono essere convogliate verso un'unica linea di uscita (bus)

# **Multiplexer binario**

Se i dati A<sub>i</sub> e B sono semplici bit si parla di multiplexer binario

$$B = \sum_{i=0}^{n-1} \alpha_i \cdot A_i$$

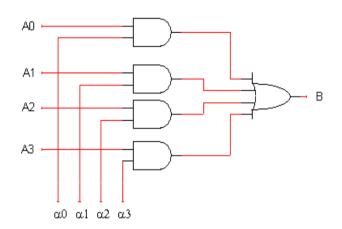

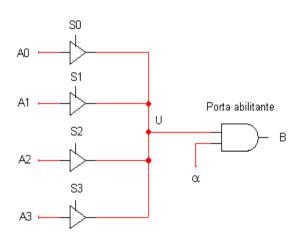

# Multiplexer binario - realizzazioni

- $B = A_0 \alpha_0 + A_1 \alpha_1 + ... + A_{n-1} \alpha_{n-1}$  n=4

- Realizzazione I

- Con porte AND e OR

- Realizzazione II

- Con porte 3-state

- S=1, restituisce il valore di A

- S=0, restituisce un'alta

| A S | Uscita | impedenza (apre il circuito) |

|-----|--------|------------------------------|

| 0 0 |        |                              |

| 0 1 | 0      |                              |

| 1 0 | Z      |                              |

| 1 1 | 1      |                              |

# Multiplexer (indirizzabile)

Multiplexer Lineare i cui segnali di abilitazione sono collegati con le uscite di un decodificatore

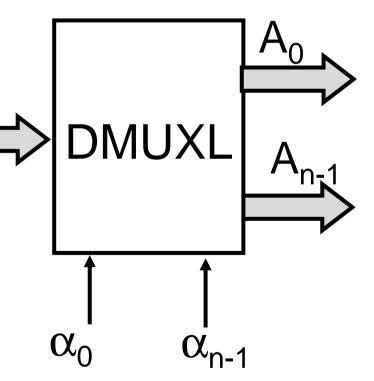

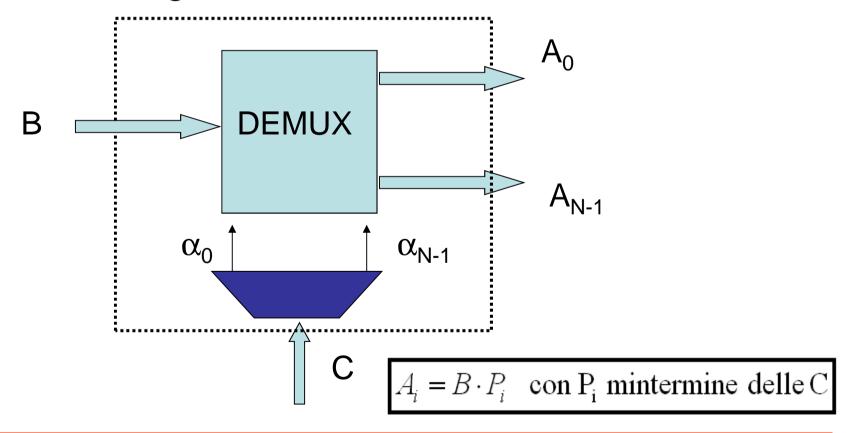

## Demultiplexer lineare

- Un Demultiplexer Lineare è una macchina con:

- 1 ingresso-dati B

- n segnali binari di selezione

(α<sub>0</sub>,..., α<sub>n-1</sub>), dei quali al più uno è attivo

- n uscite-dati  $(A_0,...,A_{n-1})$ , con

- A<sub>i</sub>=B se è attivo α<sub>i</sub>

- neutro se nessuna delle selezioni è attiva

# Demultiplexer (indirizzabile)

Demultiplexer Lineare i cui segnali di abilitazione sono collegati con le uscite di un decodificatore

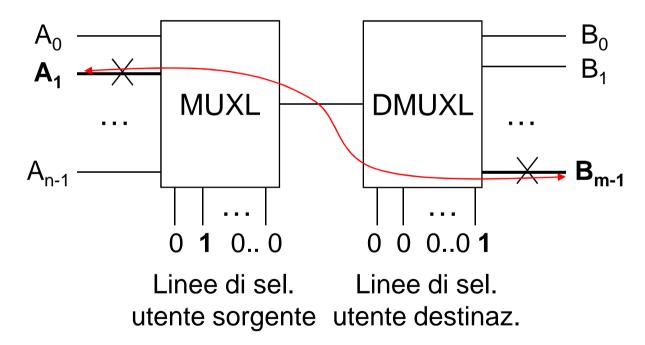

# Muxl/Dmuxl: un esempio

- Supponiamo di avere un "centralino telefonico" in cui n utenti sorgente vogliono parlare con m utenti destinazione

- vincolo: l'utente di destinazione abilitato deve sentire solo l'utente sorgente abilitato

L'utente A<sub>1</sub> è abilitato a parlare con l'utente B<sub>m-1</sub>