CAD Tools for Photonic Networks-on-Chip

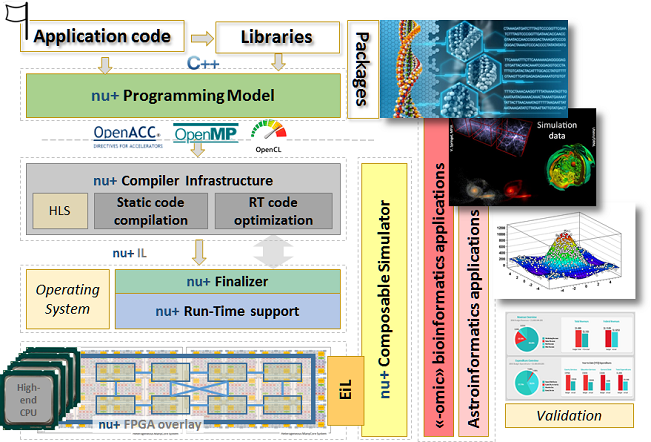

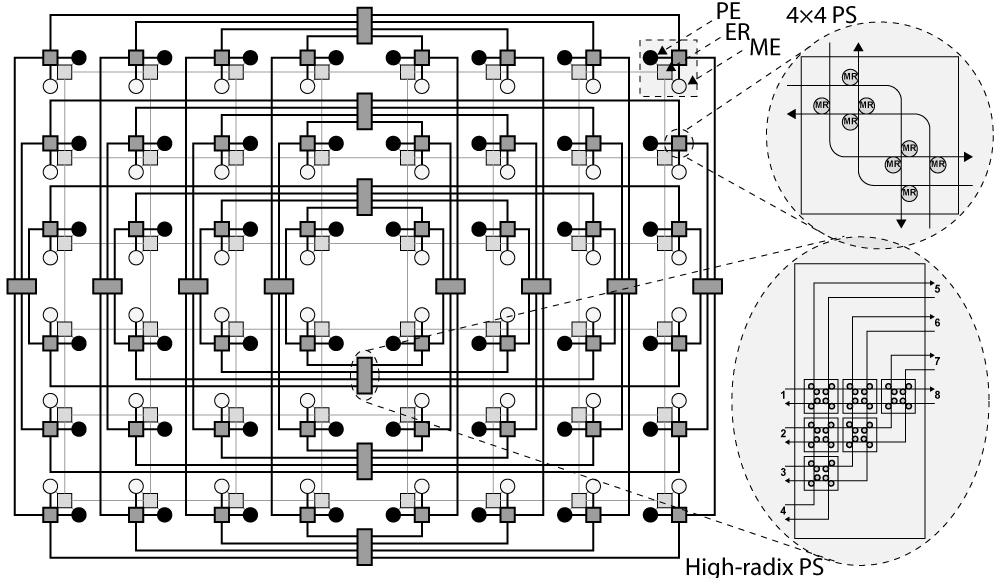

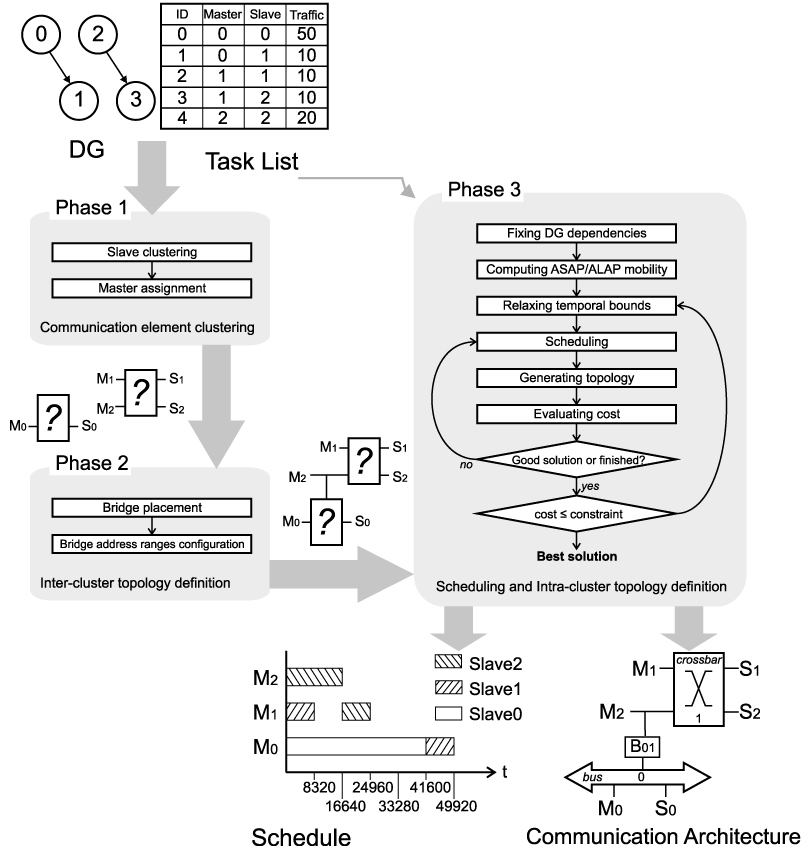

The continuous growth in application performance requirements has drastically changed the scale of multiprocessor systems-on-chip (MPSoCs). Current highly parallel MPSoCs consist of tens to hundreds of cores on a single die, requiring a high-bandwidth, low-latency and energy-efficient network-on-chip (NoC). As the network scales up, traditional electronic interconnects fail in fulfilling these requirements: at the deep submicron scale, metallic interconnects are susceptible to non-negligible parasitic resistance and capacitance resulting in poor performance and energy efficiency. Silicon photonics has generated an increasing interest over the last few years for optical interconnects in integrated circuits, providing a promising answer to effectively face the power wall, today seriously limiting further technology advances. However, to realize the potential of on-chip photonic communication to the fullest, we will thus need dedicated computer-aided design tools, just like the electronic case. The research objective of this project is to design novel CAD tools for automated photonic NoC architecture exploration and synthesis. In that respect, PhoNoCMap, our mapping tool for photonic networks-on-chip is now available for download.

The continuous growth in application performance requirements has drastically changed the scale of multiprocessor systems-on-chip (MPSoCs). Current highly parallel MPSoCs consist of tens to hundreds of cores on a single die, requiring a high-bandwidth, low-latency and energy-efficient network-on-chip (NoC). As the network scales up, traditional electronic interconnects fail in fulfilling these requirements: at the deep submicron scale, metallic interconnects are susceptible to non-negligible parasitic resistance and capacitance resulting in poor performance and energy efficiency. Silicon photonics has generated an increasing interest over the last few years for optical interconnects in integrated circuits, providing a promising answer to effectively face the power wall, today seriously limiting further technology advances. However, to realize the potential of on-chip photonic communication to the fullest, we will thus need dedicated computer-aided design tools, just like the electronic case. The research objective of this project is to design novel CAD tools for automated photonic NoC architecture exploration and synthesis. In that respect, PhoNoCMap, our mapping tool for photonic networks-on-chip is now available for download.