A.A. 2017-18

AVVISO: E' opportuno che gli studenti che seguono il corso di Calcolatori Elettronici I del prof. Canonico si iscrivano al corso sul sito

http://www.docenti.unina.it/roberto.canonico

mediante la apposita procedura, selezionando lopzione "Iscrizione alla mailing list" per ricevere eventuali comunicazioni dal docente.

Programma dettagliato delle lezioni svolte

Le slide delle lezioni (quando utilizzate) verranno pubblicate in formato PDF dopo ciascuna lezione.| Lezione | Data | Slide / Riferimenti | Argomenti |

| 1 | 05/03/2018 | Introduzione al Corso. Brevi cenni storici sulla evoluzione dei calcolatori elettronici. Primi cenni introduttivi sulla architettura di un calcolatore elettronico. |

|

| 2 | 06/03/2018 | Informazione e sua rappresentazione. Codici a lunghezza fissa ed a lunghezza variabile. Codici binari. Esempi di codici. Rappresentazione posizionale dei numeri. Sistemi binario, ottale ed esadecimale. Rappresentazione di numeri naturali. Rappresentazione di numeri interi relativi: rappresentazione in segno e modulo ed in complementi. Rappresentazione in complementi alla base. Funzione resto-modulo-M. Algoritmi di complementazione. Estensione della rappresentazione. Aritmetica in complementi. Overflow. |

|

| 3 | 08/03/2018 |

Rappresentazione in complementi diminuiti. Rappresentazione per eccessi (vedi slide lezione 2). Algebra di Boole. Proprietà fondamentali. Definizione di Algebra di Boole. Teorema di De Morgan ed altre proprietà dell'algebra di Boole. Modelli di algebre di Boole: algebra delle proposizioni. |

|

| 4 | 12/03/2018 | Modelli di algebre di Boole: algebra degli insiemi ed algebra dei circuiti (vedi slide lezione 3). Porte logiche elementari e loro composizione. Funzioni booleane e tabella di verità. Funzioni booleane di 2 variabili. Clausole e fattori elementari. Mintermini e maxtermini. Forma normale di tipo P e di tipo S di una funzione booleana. |

|

| 5 | 13/03/2018 |

Implicanti di una funzione. Generazione di consensi tra mintermini. Implicanti primi. Mappe di Karnaugh. Rappresentazione di clausole sulle Mappe di Karnaugh. Individuazione degli implicanti primi sulle mappe di Karnaugh. |

|

| 6 | 15/03/2018 | Introduzione al problema della minimizzazione di funzioni booleane. Metriche per la misura del costo di una funzione: costo di porte, costo di letterali, costo di ingressi. Ricerca dei primi implicanti: espansione sulle mappe di Karnaugh per funzioni fino a 4 variabili. Primi implicanti essenziali. Funzioni cicliche. Copertura mediante mappe di Karnaugh e mediante matrice di copertura. Semplificazione della matrice di copertura: righe e colonne dominanti. |

|

| 7 | 19/03/2018 |

Minimizzazione di funzioni booleane. Espansione ed individuazione dei primi implicanti essenziali sulle mappe di Karnaugh per una funzione di 5 variabili. Espansione con il metodo di McCluskey. |

|

| 8 | 20/03/2018 |

Funzioni incompletamente specificate. Minimizzazione di funzioni incompletamente specificate con le mappe di Karnaugh e con la matrice di copertura. Progetto di un transcodificatore per display a 7 segmenti. Funzioni NAND e NOR. Proprietà di NAND e NOR. |

|

| 9 | 22/03/2018 |

Forme NAND e NOR di una funzione booleana (vedere slide lezione precedente). Macchine combinatorie fondamentali: half e full adder. |

|

| 10 | 26/03/2018 |

Effetti dei ritardi nelle macchine combinatorie. Alee in reti combinatorie: alee statiche e dinamiche. Addizionatore binario parallelo a propagazione del riporto (vedere slide lezione precedente). Addizionatore binario con anticipo del riporto: rete di carry look-ahead. |

|

| 11 | 27/03/2018 |

Encoder e decoder. Composizione di decoder. Arbitro di priorità. Comparatore di uguaglianza. Multiplexer e demultiplexer lineari ed indirizzabili. |

|

| 12 | 05/04/2018 |

Macchine combinatorie: reti universali. Realizzazione di macchine combinatorie mediante multiplexer, ROM o PLA. Automi a stati finiti. Modelli di Moore e di Mealy. Rappresentazione di ASF mediante tabelle e mediante grafi. Macchine sequenziali. Def. di stato stabile sotto un dato ingresso. Macchine sequenziali asincrone: definizione. |

|

| 13 | 09/04/2018 |

Macchine sequenziali asincrone: modello fondamentale. Il flip flop RS fondamentale come macchina asincrona. Circuito a NOR ed a NAND: analisi. Problemi di tempificazione del flip-flop RS fondamentale. Flip-flop RS abilitato latch. |

|

| 14 | 10/04/2018 |

Flip-flop D latch. Tempificazione dei flip-flop: latch ed edge-triggered. Flip-flop RS e D edge-triggered: tabella delle transizioni di stato e circuito. |

|

| 15 | 12/04/2018 |

Flip-flop JK e T. Macchine sequenziali sincrone. Tabelle di transizione e schema realizzativo. Metodologia di progetto delle reti sincrone. Introduzione ai contatori sincroni. Progetto di un contatore sincrono mod-8 con FF e.t. di tipo D. Tabella di eccitazione di un FF di tipo D. |

|

| 16/04/2018 | LEZIONE ANNULLATA. | ||

| 16 | 17/04/2018 |

Il simulatore di reti logiche Logisim. Analisi di alcuni circuiti con Logisim. Tabelle di eccitazione dei FF di tipo JK e T. Progetto di un contatore sincrono mod-16 con FF e.t. di tipo JK. Progetto di contatori a crescere ed a decrescere (up/down). Progetto di un contatore sincrono mod-10 con FF e.t. di tipo JK e con FF di tipo T. Consultazione di datasheet di componenti commerciali. |

|

| 17 | 19/04/2018 |

Ingressi di posizionamento asincroni dei flip-flop commerciali. Contatori sincroni: ingressi di reset e precaricamento sia sincrono che asincrono. Riduzione del modulo di un contatore mediante precaricamento o reset sincrono. Progetto di una macchina sequenziale sincrona (cfr. esercizio 1 della prova intracorso dell'a.a. 2016/2017. |

|

| 18 | 23/04/2018 |

Contatori sincroni composti. Contatore mod-256. Contatore decadico mod-100. Contatore mod-24. Progetto di un riconoscitore di sequenza 1100 sincrono. |

|

| 19 | 24/04/2018 |

|

Concetto di equivalenza e compatibilità tra stati. Minimizzazione degli stati con il metodo di Paull-Unger per macchine completamente specificate. Riconoscitore di codice 8421: minimizzazione degli stati. |

| 20 | 26/04/2018 |

Riconoscitore di codice 8421: progetto della rete sequenziale. Esercizio di analisi di una rete sincrona. Realizzazione di un decoder per composizione mediante struttura ad albero. Contatori asincroni (ripple counter). |

|

| 30/04/2018 | LEZIONE ANNULLATA. | ||

| 21 | 03/05/2018 |

Definizione di compatibilità tra stati in una macchina sequenziale incompletamente specificata. Registri sincroni: parallel-in/parallel-out, serial-in/serial-out, serial-in/parallel-out. Registri a scorrimento circolare. Contatore di Johnson. Uso di multiplexer in registri a scorrimento shift/right. Esercizio di minimizzazione degli stati di una macchina sequenziale completamente specificata mediante il metodo di Paull-Unger. Esercizio di minimizzazione in forma S (prodotto di somme) di una funzione booleana incompletamente specificata. |

|

| 22 | 07/05/2018 |

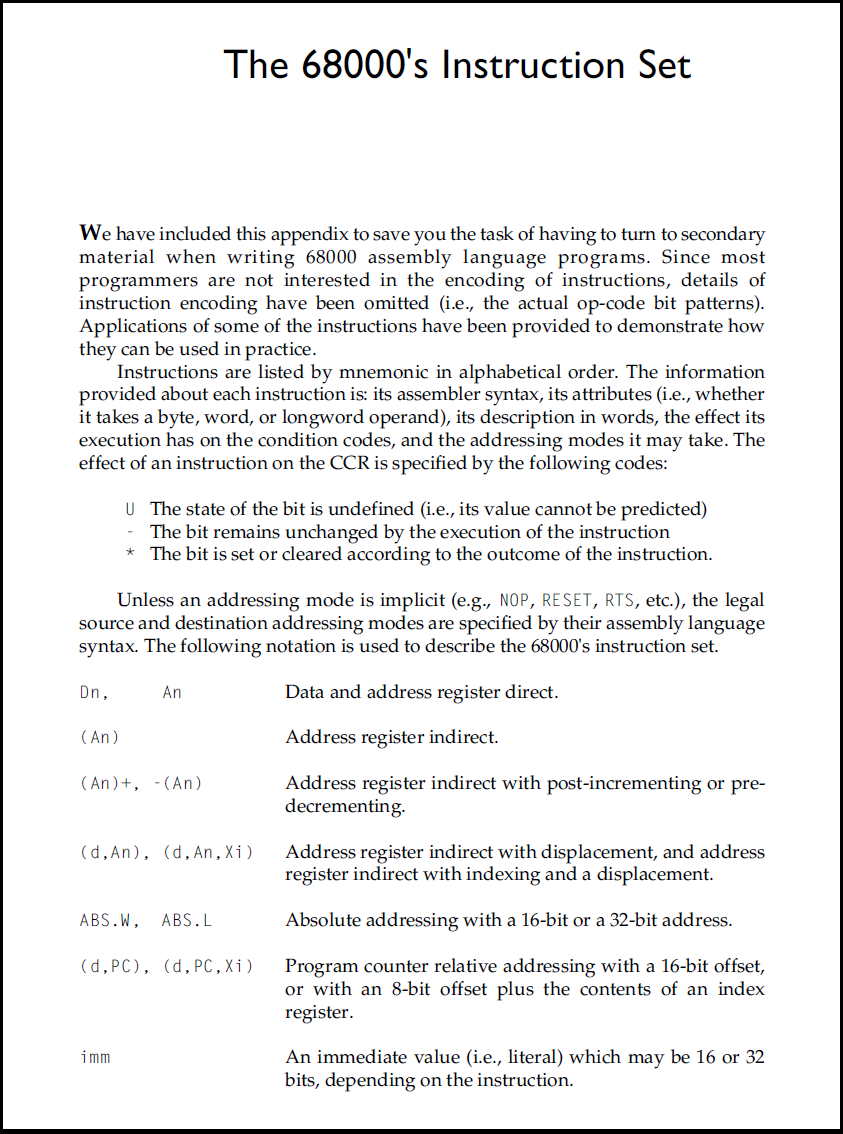

Introduzione all'architettura del calcolatore. Il processore. Ciclo del processore. Interfacciamento processore-memoria. Processore: modello ad accumulatore e modello a registri generali. Primi esempi di codici in linguaggio macchina per processori ad accumulatore ed a registri generali. Il modello di programmazione del processore Motorola MC68000. |

|

| 23 | 08/05/2018 |

Rappresentazione in memoria di dati di tipo word: disposizione big-endian e little-endian. Word allineate e non allineate. Codifica delle istruzioni in linguaggio macchina. Introduzione al linguaggio macchina. Classi di istruzioni l/m. |

|

| 24 | 09/05/2018 | PROVA INTRACORSO. | |

| 25 | 10/05/2018 |

Introduzione al linguaggio assembly. Formato delle istruzioni in assembly. Primi esempi di programmi in linguaggio assembly. Modi di indirizzamento: diretto a registro, assoluto ed immediato. Primi esempi di programmi assembly MC68000 e loro esecuzione in Asim. |

|

| 26 | 14/05/2018 |

Intruduzione al linguaggio assembly MC68000. Direttive di assemblaggio: ORG, END, EQU, DC, DS. Funzionamento dell'assemblatore. Tabella dei simboli. Assemblaggio in due passi. Manuale assembler del processore MC68000. AsimTool. Ambiente di simulazione Asim. |

|

| 27 | 15/05/2018 |

Modi di indirizzamento: diretto a registro, assoluto ed immediato, indiretto, indiretto con predecremento, indiretto con postincremento. Istruzioni in l/m e settaggio dei flag. Esempi di programmi assembly MC68000: prodotto di due numeri interi tramite somme successive, prodotto scalare di vettori di interi. |

|

| 28 | 17/05/2018 |

Istruzioni aritmetiche, logiche, di comparazione e salto del processore MC68000. Flag del processore e loro settaggio da parte delle istruzioni aritmetiche e di comparazione. Istruzioni di salto assoluto (jump) e salto relativo (branch): differenze nella codifica in linguaggio macchina. Istruzioni di salto condizionato (Bcc) del processore MC68000. Codifica in assembler MC68000 di un costrutto di selezione (if). |

|

| 29 | 21/05/2018 |

Codifica in assembler di tipici costrutti di controllo del flusso di programma. Istruzione LEA. MC68000: modi di indirizzamento avanzati: Indirect with displacement, Indirect with displacement and index. |

|

| 30 | 22/05/2018 |

Gestione di uno stack attraverso i modi di indirizzamento con predecremento e postincremento. Gestione dei sottoprogrammi in linguaggio macchina: problema del collegamento e del passaggio dei parametri. Uso dello stack per il collegamento. Uso dello stack per l'allocazione del record di attivazione. Frame pointer. MC68000: istruzioni JSR, RTS, LINK, UNLK, MOVEM. |

|

| 31 | 24/05/2018 |

Esercizi di programmazione assembler MC68000: ricerca di un token in una stringa, trasformazione lettere minuscole in maiuscole in una stringa di caratteri (touppercase). Esecuzione di programmi con subroutine nel simulatore ASIM. |

|

| 32 | 28/05/2018 |

Gerarchia di memorie in un calcolatore. Memorie indirizzabili vs. memorie content-addressable. Memorie RAM. Schemi di selezione. Selezione lineare e semiselezione. SRAM vs. DRAM. Collegamenti di chip di memoria per aumentare la capacità. Interfacciamento CPU-memoria. Schemi asincroni e sincroni. SDRAM. Analisi del codice assembly MC68000 prodotto da un compilatore C (file programmi-C.zip). Breve presentazione dei processori ARM (cenni). |

|

| 33 | 29/05/2018 |

Il sistema delle interruzioni. Interruzioni vettorizzate ed autovettorizzate. Il sistema delle interruzioni del processore MC68000. Istruzione RTE. Livelli di privilegio del processore MC68000. |

|

| 34 | 31/05/2018 |

Identificazione della richiesta di interruzione: daisy chaining, polling o handshaking. Interrupt, eccezioni e trap. Istruzioni del processore MC68000: AND, OR, NOT, EOR. Istruzione NEG. |

|

| 35 | 04/06/2018 |

Architettura interna della CPU. Cenni al ruolo della unità di controllo della CPU. Analisi della fase fetch del processore. Aritmetica in precisione multipla: istruzione ADDX. Altre istruzioni del processore MC68000: BSET, BTST, ASL, ASR, LSL, LSR, ROL, ROR. |

|

| 36 | 05/06/2018 |

Il sistema di I/O. I/O memory mapped vs. I/O isolato. Sincronizzazione del colloquio CPU-periferica: I/O programmato, I/O con interruzioni. Esempio di driver con I/O programmato e con interruzioni. Interfacce con capacità DMA. |